## Scaling ECC Hardware to a Minimum

#### Workshop CRASH 2005

CRyptographic Advances in Secure Hardware

September 6<sup>th</sup>-7<sup>th</sup> 2005, Leuven (Belgium).

Johannes.Wolkerstorfer@iaik.tugraz.at

Institute for Applied Information Processing and Communications (IAIK) — <u>VLSI Group</u>

Faculty of Computer Science Graz University of Technology

#### Outline

- Motivation

- Short introduction to ECC

- Implementation options of ECC (hardware)

- Optimization goals

- Design methodology

- ECC processor suitable for RFID

VLSI

Conclusions and future directions

## Motivation

- Small ECC hardware: What for?

- Application

- Authentication of small devices

- RFID tags: Privacy, anti forgery

- Security of sensor network nodes

- Secure wireless communication

- Goals

VLSI

- Low power

- Low die size

- Implementation security

- Alternatives

- Symmetric crypto: Key distribution issue

- Other algorithms: RSA, XTR, NTRU

## **Elliptic-Curve Cryptography**

- Protocol

- Challenge-response authentication

- Algorithm

VLSI

- ECDSA: elliptic-curve digital signature algorithm

- Computation

- Scalar multiplication

- Repeated Doubling and addition of curve points

- Finite-field operations (160-bit ... 256-bit)

IAIK

ECDSA e = SHA-1(Message)

$s = k^{-1} \cdot (e + d \cdot r)$   $2 \cdot P_1 = 2 \cdot (x_1, y_1, z_1) = (x_3, y_3, z_3) = P_3$   $x_3 = (3x_1^2 + az_1^4)^2 - 8x_1y_1^2$   $y_3 = (3x_1^2 + az_1^4)(4x_1y_1^2 - x_3) - 8y_1^4$   $z_3 = 2y_1z_1$

$\mathbf{r} = \mathbf{R}_{\mathbf{v}} \mod \mathbf{n}$

k = random(1, n-1) R = k\*(P<sub>x</sub>,P<sub>y</sub>) = (R<sub>x</sub>,R<sub>y</sub>)

Message

C C

## Elliptic-Curve Cryptography Implementation Options

- Many options to implement ECC

- Elliptic curves

VLSI

- Elliptic curves, hyper-elliptic curves

- Scalar multiplication

- Many algorithms: double-and-add, Montgomery method, NAF, window, comb, ...

- Point operations: addition and doubling

- Many point representations: affine, projective, mixed

- Finite-field arithmetic

- Prime fields GF(p): modular integer arithmetic

- Different representations: Montgomery, redundant, signed, .

- Simplifications: generalized Mersenne primes

- Binary fields GF(2<sup>m</sup>): modular polynomial arithmetic

- Different bases: polynomial, normal, optimal normal, ...

- Simplifications: trinomials, pentanomials

- Other fields: optimal extension fields OEF

#### **Designing ECC hardware is not straight-forward!**

> 30

#### TUG

IAIK

## **Requirements of Small Devices** (Passively Powered Tags)

- Area

- Determines cost

- Maximum size depends on added value

- Microcontroller too large

- Power

VLSI

- More stringent than area

- Power more important than energy

- Low clock frequency

- Power ctd.

- Excessive peak power shortens operating range

#### TUG

IAIK

## **Requirements of Small Devices** (Passively Powered Tags)

- Performance

- Low clock frequency = low throughput

- Bandwidth

VLSI

- Kilobits / second

- Many short messages more costly

- than a few long messages

- Half duplex; Reader talks first

- Security

- Robustness against side-channels attacks

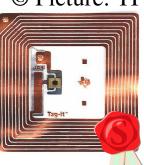

## Optimization Goals ECC for Passive Tags

- ECC for 13.56 MHz RFID tags

- Area

- Less than 1 mm<sup>2</sup>

- Power

- Passively powered

- I < 10 μA @1.5 V</li>

- To guarantee 1 m operating range

- Performance

- 300 µs

VLSI

- Security:

- ECC > 160-bit

- GF(2<sup>191</sup>)

- GF(p<sub>192</sub>)

- Manageable control

© Picture: ippaper.com

# **Design Methodology**

- Top-down design methodology

- Design space exploration

- Evaluation of design options

- Optimization for target application

- Focus on

- High-level models

- Early estimates

- Parameterizable VHDL

- Target technology

VLSI

- Standard-cell circuit

- Mixed-signal technology

- 0.35 μm 180 nm CMOS

VLSI Group, Johannes.Wolkerstorfer@iaik.tugraz.at

NV-RAM available

## ECC Hardware Scaling ECC to a Minimum

- Which functionality?

- Scalability?

- Different curves?

- Different fields

- Dual field?

- DPA resistance

- ECIES-dec only!

- Tricks applicable?

- Pre-computation?

- Early computation!

- What ECC hardware?

- Instruction set extension

- MAC unit

- Finite-field coprocessor

- EC processor

VLSI

- What in hardware?

- Multiplier!

- Full precision!

- Bit serial!

- Adder / Subtractor!

- Squarer?

- Inversion unit?

- Modular reduction!

- Fixed modulus or

- Montgomery mult.

- Memory

- Register file

- RAM

- Programmable control?

#### Explore your needs early!

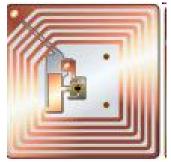

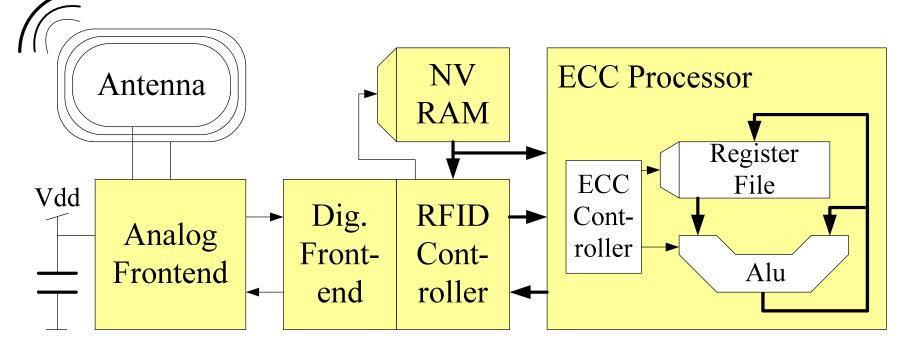

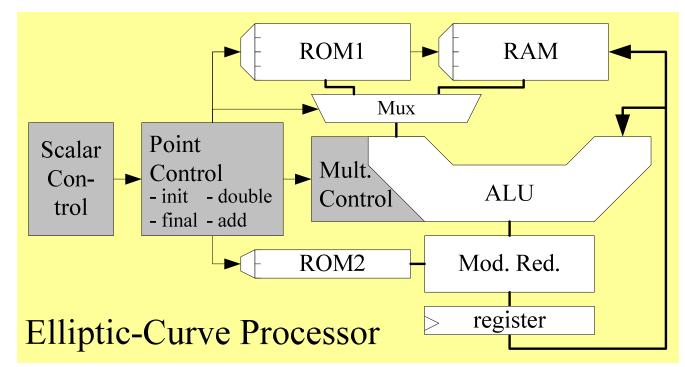

#### Architecture ECC-Enabled RFID Tag

- Conventional tag architecture

- Plus ECC processor

VLSI

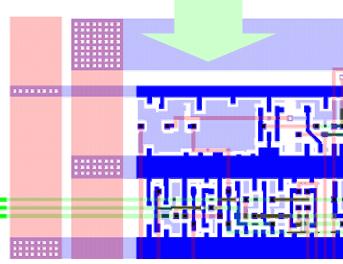

### Architecture ECC Processor: ECCU

- Full-precision architecture

- Supports different finite fields

VLSI

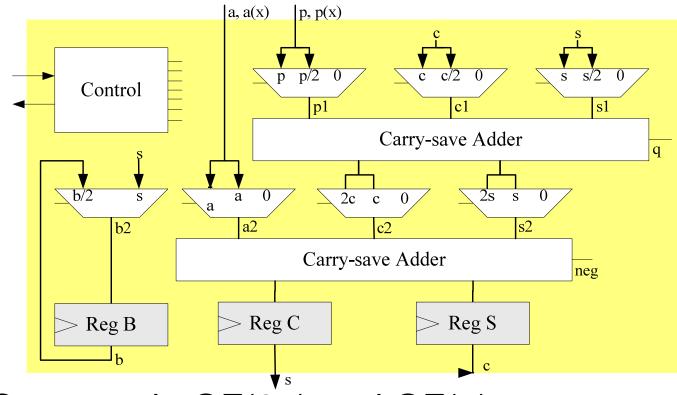

### Architecture Dual-Field Arithmetic Unit

- Operates in GF(2<sup>m</sup>) and GF(p)

- Redundant representation of GF(p)

VLSI

## **Results: Arithmetic unit**

- Operations supported by arithmetic unit

- Many HW resources reused

VLSI

|   | Name             | <i>Function</i><br>(s,c)= | Name             | <i>Function</i><br>(s,c)=           |

|---|------------------|---------------------------|------------------|-------------------------------------|

| - | Clear            | (0, 0)                    |                  |                                     |

|   | Hold             | (s', c')→(s'', 0)         | Load             | (a, 0)                              |

|   | Add              | (s+a, c)                  | Sub              | (s-a, c)                            |

|   | Shftl            | (2s, 2c)                  | Shftr            | ((s+p·q)/2, c/2)                    |

|   | Mul <sub>o</sub> | (a·b <sub>0</sub> , 0)    | Mul <sub>i</sub> | ((s+p·q)/2+a·b <sub>i</sub> +, c/2) |

- Dual-field capability at almost no overhead

- Uses Montgomery multiplication

#### **Results**

Cycle Count

VLSI

#### Area (0.35 µm CMOS)

IAIK

| Field            | Mul | Inv  | EC   |  |

|------------------|-----|------|------|--|

| р <sub>192</sub> | 197 | 11k2 | 677k |  |

| р <sub>224</sub> | 229 | 14k4 | 905k |  |

| р <sub>256</sub> | 261 | 17k7 | 1M1  |  |

| 2 <sup>191</sup> | 197 | 6k2  | 426k |  |

| 2 <sup>233</sup> | 241 | 7k5  | 635k |  |

| 2 <sup>283</sup> | 289 | 8k8  | 920k |  |

| Size<br>[bit] | Area<br>[mm²]                | Gates<br>[GE] |

|---------------|------------------------------|---------------|

| 192           | <b>1.31</b><br>0.45+0.66+0.2 | 23k           |

| 224           | <b>1.51</b><br>0.54+0.77+0.2 | 27k           |

| 256           | <b>1.71</b><br>0.62+0.89+0.2 | 31k           |

ALU + RAM + Control

### Results On Actual CMOS Processes

Size, performance, and power

| CMOS                      | ECC Processor (196-bit) |                   |                           |              |  |  |

|---------------------------|-------------------------|-------------------|---------------------------|--------------|--|--|

| l <sub>gate</sub><br>[nm] | Area<br>[mm²]           | Power<br>[µW/MHz] | f <sub>max</sub><br>[MHz] | EC<br>[kP/s] |  |  |

| 350                       | 1.31                    | 500               | 68.5                      | 101.1        |  |  |

| 180                       | 0.35                    | 170               | 225                       | 332.1        |  |  |

| 90                        | 0.09                    | 55                | 600                       | 885.6        |  |  |

- Most efficient ECC processor (area)

- Reported in literature so far!

### Results Does ECCU fit RFID?

- Area on 0.35 µm CMOS

- No too large: 1.31 mm<sup>2</sup>

- Area on 180 nm CMOS

- YES 0.35 mm<sup>2</sup> is realistic

- Power

VLSI

- YES! Constraints can be met by

- Lowering clock frequency (e.g. 175 kHz @180 nm)

- Performance (@ 180 nm)

- Poor on RFIDs: > 1 second (@ 175 kHz)

- But: 330 ops / second (@ f<sub>max</sub> = 225 MHz)

## Conclusions

- Thorough analysis

- Many choices for ECC

- Tailored hardware!

- Achievements

- Novel arithmetic unit

- Dual-field operation: GF(p) and GF(2<sup>m</sup>)

- Area (and power consumption)

- Suitable for RFID implementation

- Outlook

- Hardwired control

- More efficient register file

### Future directions ECC Hardware

- Challenges to solve

- Problems of ECC

- Too many standards

- Restriction to prime fields useful?

- Unclear situation with patents

- Hashes

- Bulky HW implementation

- Protocols

- Authentication protocols

- Without hashes

- Standards